Standard Wafer sizesEdit

SiliconEdit

Siliziumwafer sind in einer Vielzahl von Durchmessern von 25,4 mm (1 Zoll) bis 300 mm (11,8 Zoll) erhältlich. Halbleiterfertigungsanlagen, umgangssprachlich Fabs genannt, werden durch den Durchmesser der Wafer definiert, zu deren Herstellung sie bearbeitet werden. Der Durchmesser wurde schrittweise erhöht, um den Durchsatz zu verbessern und die Kosten mit der aktuellen hochmodernen Fabrik mit 300 mm zu senken, mit einem Vorschlag zur Einführung von 450 mm. Intel, TSMC und Samsung forschten getrennt nach dem Aufkommen von 450 mm „Prototyp“ (Forschungs-) Fabs, obwohl ernsthafte Hürden bestehen bleiben.

| Wafergröße | Typische Dicke | Jahr eingeführt | Gewicht pro Wafer | 100 mm2 (10 mm) Sterben pro Wafer |

|---|---|---|---|---|

| 1 Zoll (25 mm) | 1960 | |||

| 2 Zoll (51 mm) | 275 µm | 1969 | ||

| 3 Zoll (76 mm) | 375 μm | 1972 | ||

| 4-inch (100 mm) | 525 μm | 1976 | 10 grams | 56 |

| 4.9 inch (125 mm) | 625 μm | 1981 | ||

| 150 mm (5.9 inch, usually referred to as „6 inch“) | 675 μm | 1983 | ||

| 200 mm (7.9 inch, usually referred to as „8 inch“) | 725 μm. | 1992 | 53 grams | 269 |

| 300 mm (11.8 zoll, in der regel bezeichnet als „12 zoll“) | 775 µm | 2002 | 125 gramm | 640 |

| 450mm (17,7 zoll) (vorgeschlagen) | 925 µm | – | 342 gramm | 1490 |

| 675 Millimeter (26,6 Zoll) (theoretisch) | Unbekannt. | – |

Wafer, die mit anderen Materialien als Silizium gezüchtet werden, haben unterschiedliche Dicken als Siliziumwafer mit demselben Durchmesser. Die Waferdicke wird durch die mechanische Festigkeit des verwendeten Materials bestimmt; der Wafer muss dick genug sein, um sein eigenes Gewicht zu tragen, ohne während der Handhabung zu reißen. Die tabellarischen Dicken beziehen sich darauf, wann dieser Prozess eingeführt wurde, und sind derzeit nicht unbedingt korrekt, zum Beispiel ist der IBM BiCMOS7WL-Prozess auf 8 in Wafern, aber diese sind nur 200um dick. Das Gewicht des Wafers steigt mit seiner Dicke und seinem Durchmesser.

Historische Zunahme der Wafergrößebearbeiten

Ein Schritt zur Herstellung von Einheitswafern, beispielsweise ein Ätzschritt, kann proportional zur Zunahme der Waferfläche mehr Chips produzieren, während die Kosten für den Schritt zur Herstellung von Einheitswafern langsamer steigen als die Waferfläche. Dies war die Kostenbasis für die Erhöhung der Wafergröße. Die Umstellung auf 300-mm-Wafer von 200-mm-Wafern begann ernsthaft im Jahr 2000 und reduzierte den Preis pro Würfel um 30-40%. Wafer mit größerem Durchmesser ermöglichen mehr Die pro Wafer.

PhotovoltaicEdit

Die M1-Wafergröße (156,75 mm) wird in China ab 2020 auslaufen. Eine Reihe von Nicht-Standard-Größen entstanden ist, so dass die Bemühungen M10 Standard (182 mm) zu produzieren, ist eine laufende Anstrengung. Wie bei Halbleitern ist die Senkung der Kosten der Haupttreiber, obwohl die Reinheitsanforderungen völlig unterschiedlich sind.

Vorgeschlagener 450-mm-Übergang

Trotz der möglichen Produktivitätsverbesserung gibt es erheblichen Widerstand gegen den 450-mm-Übergang, da Bedenken hinsichtlich einer unzureichenden Kapitalrendite bestehen. Es gibt auch Probleme im Zusammenhang mit einer erhöhten Inter-Die / Edge-to-Edge-Wafer-Variation und zusätzlichen Kantenfehlern. Es wird erwartet, dass 450-mm-Wafer 4-mal so viel kosten wie 300-mm-Wafer, und die Ausrüstungskosten werden voraussichtlich um 20 bis 50% steigen. Höhere Kosten Halbleiterfertigungsausrüstung für größere Wafer erhöht die Kosten von 450 mm Fabs (Halbleiterfertigungsanlagen oder Fabriken). Der Lithograf Chris Mack behauptete 2012, dass der Gesamtpreis pro Chip für 450-mm-Wafer im Vergleich zu 300-mm-Wafern nur um 10-20% gesenkt würde, da über 50% der gesamten Waferverarbeitungskosten lithographiebezogen sind. Die Umstellung auf größere 450-mm-Wafer würde den Preis pro Chip nur für Prozessvorgänge wie das Ätzen senken, bei denen die Kosten mit der Waferanzahl und nicht mit der Waferfläche zusammenhängen. Die Kosten für Prozesse wie die Lithographie sind proportional zur Waferfläche, und größere Wafer würden den Lithographiebeitrag zu den Düsenkosten nicht verringern. Nikon plante die Auslieferung von 450-mm-Lithografiegeräten im Jahr 2015 mit einer Serienproduktion im Jahr 2017. Im November 2013 unterbrach ASML die Entwicklung von 450-mm-Lithografiegeräten unter Berufung auf den unsicheren Zeitpunkt der Nachfrage der Chiphersteller.

Der Zeitplan für 450 mm wurde nicht festgelegt. Im Jahr 2012 wurde erwartet, dass die 450-mm-Produktion im Jahr 2017 beginnen würde, was nie realisiert wurde. Mark Durcan, damals CEO von Micron Technology, sagte im Februar 2014, dass er erwartet, dass die Einführung von 450 mm auf unbestimmte Zeit verzögert oder eingestellt wird. „Ich bin nicht davon überzeugt, dass 450 mm jemals passieren werden, aber in dem Maße, wie es der Fall ist, ist es ein langer Weg in die Zukunft. Es gibt nicht viel Notwendigkeit für Micron, zumindest in den nächsten fünf Jahren, eine Menge Geld für 450mm auszugeben. Es gibt eine Menge Investitionen, die in der Ausrüstungsgemeinschaft getätigt werden müssen, um dies zu erreichen. Und der Wert am Ende des Tages – damit die Kunden diese Ausrüstung kaufen würden – halte ich für zweifelhaft.“ Ab März 2014 erwartete die Intel Corporation den Einsatz von 450 mm bis 2020 (bis Ende dieses Jahrzehnts). Mark LaPedus von Semiengineering.com berichtete Mitte 2014, dass Chiphersteller die Einführung von 450 mm „auf absehbare Zeit“verzögert hätten.“ Laut diesem Bericht erwarteten einige Beobachter 2018 bis 2020, während G. Dan Hutcheson, Chief Executive von VLSI Research, erst 2020 bis 2025 450-mm-Fabriken in Produktion gehen sah.

Der Schritt bis zu 300 mm erforderte große Änderungen, mit vollautomatischen Fabriken mit 300-mm-Wafern im Vergleich zu kaum automatisierten Fabriken für die 200-mm-Wafer, teilweise weil eine FOUP für 300-mm-Wafer wiegt etwa 7,5 Kilogramm, wenn sie mit 25 300-mm-Wafern beladen ist, wo ein SMIF etwa 4 wiegt.8 kilogramm bei Beladung mit 25 200-mm-Wafern, wodurch die Fabrikarbeiter doppelt so viel körperliche Kraft benötigen und die Ermüdung zunimmt. 300mm FOULs haben Griffe, so dass sie noch von Hand bewegt werden können. 450mm FOULs wiegen 45 Kilogramm, wenn sie mit 25 450 mm Wafern beladen werden, daher sind Kräne notwendig, um die FOULs manuell zu handhaben, und Griffe sind nicht mehr in der FOUP vorhanden. FOULs werden mit Materialflusssystemen von Muratec oder Daifuku bewegt. Diese großen Investitionen wurden im wirtschaftlichen Abschwung nach der Dotcom-Blase getätigt, was zu einem enormen Widerstand gegen die Aufrüstung auf 450 mm bis zum ursprünglichen Zeitrahmen führte. Auf der Rampe – bis zu 450 mm – werden die Kristallbarren 3-mal schwerer (Gesamtgewicht eine Tonne) und brauchen 2-4-mal länger zum Abkühlen, und die Prozesszeit wird doppelt so lang sein. Alles in allem erfordert die Entwicklung von 450-mm-Wafern ein erhebliches Engineering, Zeit und Kosten.

Analytische Schätzung der Matrizenzahlbearbeiten

Um die Kosten pro Matrize zu minimieren, möchten die Hersteller die Anzahl der Matrizen maximieren, die aus einem einzelnen Wafer hergestellt werden können. Im Allgemeinen ist dies ein rechnerisch komplexes Problem ohne analytische Lösung, das sowohl von der Fläche der Matrizen als auch von ihrem Seitenverhältnis (quadratisch oder rechteckig) und anderen Überlegungen wie der Breite der Ritz- oder Sägebahn und dem zusätzlichen Raum abhängt, den Ausrichtungs- und Teststrukturen einnehmen. Beachten Sie, dass die Brutto-DPW-Formeln nur die Waferfläche berücksichtigen, die verloren geht, da sie nicht zur Herstellung physikalisch vollständiger Matrizen verwendet werden kann. Brutto-DPW-Berechnungen berücksichtigen keinen Ertragsverlust aufgrund von Defekten oder parametrischen Problemen.

Dennoch kann die Anzahl der Bruttodüsen pro Wafer (DPW) ausgehend von der Näherung erster Ordnung oder dem Wafer-zu-Die-Flächenverhältnis geschätzt werden,

D P W = ⌊ π d 2 4 S ⌋ {\displaystyle DPW=\left\lfloor {\frac {\pi d^{2}}{4S}}\right\rfloor }

,

wobei d {\displaystyle d}

der Waferdurchmesser (typischerweise in mm) und S {\displaystyle S}

die Größe jedes (mm2) einschließlich der Breite des scribeline ( oder im Falle einer Sägebahn die Schnittfuge plus Toleranz). Diese Formel besagt einfach, dass die Anzahl der Matrizen, die auf den Wafer passen können, die Fläche des Wafers geteilt durch die Fläche jedes einzelnen Stempels nicht überschreiten darf. Es wird immer den wahren Best-Case-Brutto-DPW überschätzen, da es den Bereich der teilweise strukturierten Dies umfasst, die nicht vollständig auf der Waferoberfläche liegen (siehe Abbildung). Diese teilweise gemusterten Dies stellen keine vollständigen ICs dar und können daher nicht als Funktionsteile verkauft werden. Verfeinerungen dieser einfachen Formel fügen typischerweise eine Kantenkorrektur hinzu, um Teildüsen an der Kante zu berücksichtigen, die im Allgemeinen bedeutender sind, wenn die Fläche der Düse im Vergleich zur Gesamtfläche des Wafers groß ist. Im anderen Grenzfall (infinitesimal kleine Dies oder unendlich große Wafer) ist die Kantenkorrektur vernachlässigbar.

Der Korrekturfaktor oder Korrekturterm nimmt im Allgemeinen eine der von De Vries zitierten Formen an:

D P W = π d 2 4 S − π d 2 S {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}-{\frac {\displaystyle \pi d}{\sqrt {2S}}}}

(Flächenverhältnis – Umfang/(die diagonale Länge)) oder D P W = ( π d 2 4 S ) exp ( − 2 S/d ) {\displaystyle DPW=\left({\frac {\displaystyle \pi d^{2}}{4S}}\right)\exp(-2{\sqrt {S}}/d)}

(Flächenverhältnis skaliert um ein Exponentialfaktor) oder D P W = π d 2 4 S ( 1 − 2 S d ) 2 {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}\left(1-{\frac {\displaystyle 2{\sqrt {S}}}{d}}\right)^{2}}

(Flächenverhältnis skaliert um einen Polynomfaktor).

Studien, die diese analytischen Formeln mit Brute-Force−Berechnungsergebnissen vergleichen, zeigen, dass die Formeln über praktische Bereiche von Matrizengrößen und Seitenverhältnissen genauer gemacht werden können, indem die Koeffizienten der Korrekturen auf Werte oberhalb oder unterhalb der Einheit angepasst werden und indem die lineare Matrizendimension S {\displaystyle {\sqrt {S}}}

durch ( H + W ) / 2 {\displaystyle H+W)/2}

(mittlere Seitenlänge) bei Matrizen mit großem Seitenverhältnis: D P W = π d 2 4 S – 0.58 ∗ π d S {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}-0,58^{*}{\frac {\displaystyle \pi d}{\sqrt {S}}}}

oder D P W = ( π d 2 4 S ) exp ( − 2,32 ∗ S / d ) {\displaystyle DPW=\links({\frac {\displaystyle \pi d^{2}}{4S}}\rechts)\exp(-2,32^{*}{\sqrt {S}}/d)}

oder D P W = π d 2 4 S ( 1 − 1.16 ∗ S d ) 2 {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}\links(1-{\frac {\displaystyle 1.16^{*}{\sqrt {S}}}{d}}\rechts)^{2}}

.

Kristalline Orientierungbearbeiten

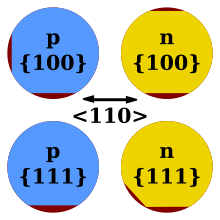

Wafer werden aus Kristallen mit regelmäßiger Kristallstruktur gezüchtet, wobei Silizium eine diamantkubische Struktur mit einem Gitterabstand von 5,430710 Å (0,5430710 nm) aufweist. Beim Schneiden in Wafer wird die Oberfläche in einer von mehreren relativen Richtungen ausgerichtet, die als Kristallorientierungen bezeichnet werden. Die Orientierung wird durch den Miller-Index definiert, wobei (100) oder (111) Flächen für Silizium am häufigsten sind.Orientierung ist wichtig, da viele der strukturellen und elektronischen Eigenschaften eines Einkristalls stark anisotrop sind. Die Tiefe der Ionenimplantation hängt von der Kristallorientierung des Wafers ab, da jede Richtung unterschiedliche Transportwege bietet.

Waferspaltung tritt typischerweise nur in wenigen genau definierten Richtungen auf. Wenn der Wafer entlang von Spaltebenen geritzt wird, kann er leicht in einzelne Chips („Dies“) zerlegt werden, so dass die Milliarden einzelner Schaltungselemente auf einem durchschnittlichen Wafer in viele einzelne Schaltungen getrennt werden können.

Kristallographische Orientierungskerbenbearbeiten

Wafer mit einem Durchmesser unter 200 mm haben Flachflächen, die in eine oder mehrere Seiten geschnitten sind, die die kristallographischen Ebenen des Wafers anzeigen (normalerweise eine {110} Fläche). Bei Wafern früherer Generationen bestimmte ein Paar von ebenen in verschiedenen Winkeln zusätzlich den Dotierungstyp (siehe Abbildung für Konventionen). Wafer mit einem Durchmesser von 200 mm und darüber verwenden eine einzige kleine Kerbe, um die Waferorientierung zu vermitteln, ohne visuelle Anzeige des Dotierungstyps.

Impurity dotingEdit

Siliziumwafer sind im Allgemeinen nicht 100% reines Silizium, sondern werden stattdessen mit einer anfänglichen Verunreinigungsdotierungskonzentration zwischen 1013 und 1016 Atomen pro cm3 Bor, Phosphor, Arsen oder Antimon gebildet, die der Schmelze zugesetzt wird und den Wafer entweder als Bulk-n-Typ oder als p-Typ definiert. Verglichen mit der Atomdichte von einkristallinem Silizium von 5 × 1022 Atomen pro cm3 ergibt dies jedoch immer noch eine Reinheit von mehr als 99,9999%. Die Wafer können auch zunächst mit einer gewissen interstitiellen Sauerstoffkonzentration versehen werden. Kohlenstoff und metallische Verunreinigungen werden auf ein Minimum reduziert. Insbesondere Übergangsmetalle müssen für elektronische Anwendungen unter der Konzentration von Teilen pro Milliarde gehalten werden.