Standard wafer sizesEdit

SiliconEdit

Silisiumskiver er tilgjengelige i en rekke diametre fra 25,4 mm (1 tommer) til 300 mm (11,8 tommer). Semiconductor fabrikasjon planter, folkemunne kjent som fabs, er definert av diameteren på wafere at de er tooled å produsere. Diameteren har gradvis økt for å forbedre gjennomstrømningen og redusere kostnadene med dagens toppmoderne fab ved hjelp av 300 mm, med et forslag om å vedta 450 mm. Intel, Tsmc og Samsung var separat drive forskning til advent av 450 mm» prototype » (forskning) fabs, selv om alvorlige hindringer forbli.

| waferstørrelse | typisk tykkelse | vekt per wafer | 100 mm2 (10 mm) dør per wafer | |

|---|---|---|---|---|

| 1 tommer (25 mm) | 1960 | 2 tommer (51 mm) | 275 µ | 1969 | 375 μm | 1972 |

| 4-inch (100 mm) | 525 μm | 1976 | 10 grams | 56 |

| 4.9 inch (125 mm) | 625 μm | 1981 | ||

| 150 mm (5.9 inch, usually referred to as «6 inch») | 675 μm | 1983 | ||

| 200 mm (7.9 inch, usually referred to as «8 inch») | 725 μm. | 1992 | 53 grams | 269 |

| 300 mm (11.8 tommer, vanligvis referert til som «12 tommer») | 775 µ | 2002 | 125 gram | 640 |

| 450 mm (17,7 tommer) (foreslått) | 925 µ | – | 342 gram | 1490 |

| 675 millimeter (26,6 tommer) (teoretisk) | ukjent. | – |

Wafere dyrket ved hjelp av andre materialer enn silisium vil ha forskjellige tykkelser enn en silisiumskive med samme diameter. Wafertykkelsen bestemmes av den mekaniske styrken til materialet som brukes; waferen må være tykk nok til å støtte sin egen vekt uten å sprekke under håndtering. Tabulert tykkelser forholde seg til når denne prosessen ble innført, og er ikke nødvendigvis riktig for tiden, FOR EKSEMPEL IBM BiCMOS7WL prosessen er på 8 i wafere, men disse er bare 200um tykk. Vekten av waferen går opp sammen med dens tykkelse og diameter.

Historiske økninger av wafer sizeEdit

en enhet wafer fabrikasjon trinn, for eksempel et ets trinn, kan produsere flere chips proporsjonal med økningen i wafer området, mens kostnaden av enheten fabrikasjon trinn går opp saktere enn wafer området. Dette var kostnadsgrunnlaget for å øke waferstørrelsen. Konvertering til 300 mm wafere fra 200 mm wafere begynte for alvor i 2000, og reduserte prisen per dør ca 30-40%. Større diameter wafers tillate mer dør per wafer.

Fotovoltaicedit

M1 wafer størrelse (156.75 mm) er i ferd med å fase ut I Kina som i 2020. En rekke ikke-standardstørrelser har oppstått, så arbeidet med å produsere m10 standard (182 mm) er en kontinuerlig innsats. Som semiconductor cousin er kjøring ned kostnader hoveddriver til tross for at renhetskravene er helt forskjellige.

Foreslått 450 mm overgangredit

det er betydelig motstand mot 450 mm overgang til tross for mulig produktivitetsforbedring, på grunn av bekymring for utilstrekkelig avkastning på investeringen. Det er også problemer knyttet til økt inter-die / kant-til-kant wafer variasjon og ytterligere kantfeil. 450mm wafers forventes å koste 4 ganger så mye som 300mm wafers, og utstyrskostnadene forventes å stige med 20 til 50%. Høyere kostnader halvleder fabrikasjon utstyr for større wafere øker kostnadene for 450 mm fabs(halvleder fabrikasjon anlegg eller fabrikker). Litograf Chris Mack hevdet i 2012 at den totale prisen per dør for 450 mm wafere ville bli redusert med bare 10-20% sammenlignet med 300 mm wafere, fordi over 50% av totale wafer behandlingskostnader er litografi-relaterte. Konvertering til større 450 mm wafere ville redusere prisen per dør bare for prosessoperasjoner som etch hvor kostnadene er relatert til wafer teller, ikke wafer området. Kostnad for prosesser som litografi er proporsjonal med wafer området, og større wafere ville ikke redusere litografi bidrag til dø kostnad. Nikon planla å levere litografiutstyr på 450 mm i 2015, med volumproduksjon i 2017. I November 2013 asml stoppet utviklingen av 450 mm litografi utstyr, siterer usikker timing av chipmaker etterspørsel.

tidslinjen for 450 mm er ikke løst. I 2012 ble det forventet at 450mm produksjonen ville starte i 2017, som aldri realiserte. Mark Durcan, DA ADMINISTRERENDE DIREKTØR I Micron Technology, sa i februar 2014 at han forventer at 450 mm adopsjon vil bli forsinket på ubestemt tid eller avviklet. «Jeg er ikke overbevist om at 450mm noen gang vil skje, men i den grad det gjør det, er det langt ut i fremtiden. Det er ikke mye nødvendighet For Micron, i hvert fall de neste fem årene, å bruke mye penger på 450mm. Det er mye investering som må fortsette i utstyrssamfunnet for å få det til å skje. Og verdien på slutten av dagen – slik at kundene ville kjøpe det utstyret-tror jeg er tvilsomt.»Fra Mars 2014 forventet Intel Corporation 450 mm distribusjon innen 2020 (innen utgangen av dette tiåret). Mark LaPedus av semiengineering.com rapporterte i midten av 2014 at chipmakers hadde forsinket adopsjon av 450 mm «i overskuelig fremtid.»Ifølge denne rapporten forventet noen observatører 2018 til 2020, Mens G. Dan Hutcheson, administrerende direktør I VLSI Research, ikke så 450mm fabs flytte inn i produksjon før 2020 til 2025.trinnet opp til 300 mm krevde store endringer, med helautomatiske fabrikker som bruker 300 mm wafers versus knapt automatiserte fabrikker for 200 mm wafers, delvis fordi EN FOUP for 300 mm wafers veier ca 7,5 kilo når lastet med 25 300 mm wafers hvor EN SMIF veier ca 4.8 kilo når lastet med 25 200 mm wafers, og dermed krever dobbelt så mye fysisk styrke fra fabrikkarbeidere, og økende tretthet. 300mm FOUPs har håndtak slik at de fortsatt kan flyttes for hånd. 450mm FOUPs veier 45 kilo når lastet med 25 450 mm wafers, og dermed kraner er nødvendig for å håndtere FOUPs manuelt og håndtak er ikke lenger til stede i FOUP. FOUPs flyttes rundt ved hjelp av materialhåndteringssystemer Fra Muratec eller Daifuku. Disse store investeringene ble foretatt i den økonomiske nedgangen etter dot-com-boblen, noe som resulterte i stor motstand mot oppgradering til 450 mm innen den opprinnelige tidsrammen. På rampen-opp til 450 mm vil krystallbøttene være 3 ganger tyngre (totalvekt et metrisk tonn) og ta 2-4 ganger lengre tid å avkjøle, og prosesstiden blir dobbel. Alt i alt krever utviklingen av 450 mm wafers betydelig engineering, tid og kostnad å overvinne.

Analytisk die count estimationEdit

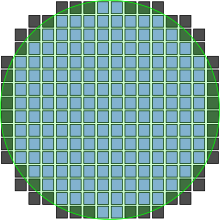

for å minimere kostnadene per dør, produsenter ønsker å maksimere antall dør som kan gjøres fra en enkelt wafer; dør har alltid en kvadratisk eller rektangulær form på grunn av begrensningen av wafer dicing. Generelt er dette et beregningsmessig komplekst problem uten analytisk løsning, avhengig av både området av dysene og deres aspektforhold (kvadratisk eller rektangulær) og andre hensyn som bredden på scribeline eller sagbanen, og ekstra plass okkupert av justering og teststrukturer. Vær oppmerksom på at brutto dpw formler konto bare for wafer området som er tapt fordi det ikke kan brukes til å gjøre fysisk fullstendig dør; brutto dpw beregninger tar ikke hensyn til yield tap på grunn av feil eller parametriske problemer.

likevel kan antall brutto dør per wafer (DPW) estimeres fra første ordens tilnærming eller wafer-til-dø-arealforholdet,

D P w = ⌊ π d 2 4 S ⌋ {\displaystyle dpw=\venstre\lfloor {\frac {\pi d^{2}}{4s}}\right\rfloor }

,

hvor d {\displaystyle d}

er waferdiameteren (typisk i mm) og s {\displaystyle s}

størrelsen på hver dør (MM2) inkludert bredden på scribeline (eller i tilfelle av en sagbane, kerf pluss en toleranse). Denne formelen sier bare at antall dør som kan passe på waferen, ikke kan overstige arealet av waferen dividert med arealet av hver enkelt dør. Det vil alltid overvurdere den sanne beste brutto dpw, siden det inkluderer området med delvis mønstrede dør som ikke helt ligger på waferoverflaten (se figur). Disse delvis mønstrede dysene representerer ikke komplette ICs, så de kan ikke selges som funksjonelle deler. Forbedringer av denne enkle formelen legger vanligvis til en kantkorreksjon, for å ta hensyn til delvise dør på kanten, som generelt vil være mer signifikant når området av dysen er stort sammenlignet med det totale arealet av waferen. I det andre begrensende tilfellet (uendelig små dør eller uendelig store wafers) er kantkorreksjonen ubetydelig.

korreksjonsfaktoren eller korreksjonsbegrepet tar vanligvis en av formene sitert Av De Vries:

d P W = π d 2 4 s − π d 2 s {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}-{\frac {\displaystyle \pi d}{\sqrt {2s}}}

(arealforhold – omkrets/(dø diagonal lengde)) ELLER d p w = ( π d 2 4 s ) exp ( − 2 s / d) {\DISPLAYSTYLE dpw=\venstre ({\frac {\displaystyle\pi d^{2}} {4S}}\høyre)\exp(-2 {\sqrt {s}}/d)}

(arealforhold skalert av en eksponentiell faktor) Eller D P w = π d 2 4 S ( 1 − 2 S d ) 2 {\displaystyle dpw={\frac {\displaystyle \pi d^{2}}{4s}}\venstre(1-{\frac {\displaystyle 2{\sqrt {s}} {d}}\høyre)^{2}}

(arealforhold skalert med en polynomfaktor).

Studier som sammenligner disse analytiske formlene med brute-force beregningsresultater viser at formlene kan gjøres mer nøyaktige, over praktiske områder av dørstørrelser og aspektforhold, ved å justere koeffisientene til korreksjonene til verdier over eller under enhet, og ved å erstatte den lineære dørdimensjonen s {\displaystyle {\sqrt {s}}}

med ( H + W)/2 {\displaystyle (h+w) / 2}

med ( H + W)/2 {\displaystyle (h+w) / 2}

(gjennomsnittlig sidelengde) ved dør med stort sideforhold: d p w = Π d 2 4 s − 0.58 ∗ π d S {\displaystyle dpw = {\frac {\displaystyle \pi d^{2}}{4s}} -0,58 ^ {*} {\frac {\displaystyle \pi d} {\sqrt {S}}}

eller d P W = ( π d 2 4 S ) exp ( − 2,32 ∗ s / d ) {\displaystyle DPW=\venstre({\frac {\displaystyle \pi d^{2}} {4S}}\høyre)\exp(-2,32^{*} {\sqrt {s}}/d)}

eller d P W = π d 2 4 S ( 1 − 1.16 ∗ s d ) 2 {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}\venstre(1-{\frac {\displaystyle 1.16^{*}{\sqrt {s}} {d}}\høyre)^{2}}

.

Krystallinsk orienteringrediger

diamant kubisk krystallstruktur av en silisiumenhetscelle

Wafer cleavage oppstår vanligvis bare i noen få veldefinerte retninger. Scoring wafer langs cleavage fly gjør det enkelt å terninger i individuelle chips («dør») slik at milliarder av individuelle kretselementer på en gjennomsnittlig wafer kan deles inn i mange individuelle kretser.

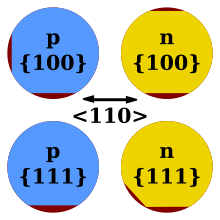

Krystallografisk orientering notchesEdit

Wafere under 200 mm diameter har leiligheter kuttet i en eller flere sider som indikerer krystallografiske fly av wafer (vanligvis en {110} ansikt). I tidligere generasjon wafere et par leiligheter i forskjellige vinkler i tillegg formidlet doping type (se illustrasjon for konvensjoner). Wafere av 200 mm diameter og over bruke et enkelt lite hakk for å formidle wafer orientering, uten visuell indikasjon på doping type.Silisiumskiver Er vanligvis ikke 100% rent silisium, Men dannes i stedet med en innledende urenhetsdopingkonsentrasjon mellom 1013 og 1016 atomer per cm3 av bor, fosfor, arsen eller antimon som tilsettes til smelten og definerer waferen som enten bulk n-type eller p-type. Men sammenlignet med enkeltkrystall silisiums atomtetthet på 5×1022 atomer per cm3, gir dette fortsatt en renhet større enn 99.9999%. Waferne kan også i utgangspunktet forsynes med noen interstitial oksygenkonsentrasjon. Karbon og metallforurensning holdes på et minimum. Overgangsmetaller, spesielt, må holdes under deler per milliard konsentrasjoner for elektroniske applikasjoner.