Standard wafer sizesEdit

SiliconEdit

I wafer di silicio sono disponibili in una varietà di diametri da 25,4 mm (1 pollice) a 300 mm (11,8 pollici). Gli impianti di fabbricazione di semiconduttori, noti colloquialmente come fab, sono definiti dal diametro dei wafer che sono utilizzati per produrre. Il diametro è gradualmente aumentato per migliorare la produttività e ridurre i costi con l’attuale fab all’avanguardia che utilizza 300 mm, con una proposta di adottare 450 mm. Intel, TSMC e Samsung stavano conducendo separatamente la ricerca per l’avvento di 450 mm “prototipo” (ricerca) fab, anche se gravi ostacoli rimangono.

| Wafer di dimensioni | Spessore Tipico | Anno di introduzione | Peso per wafer | 100 mm2 (10 mm) Die per wafer |

|---|---|---|---|---|

| 1-pollice (25 mm) | 1960 | |||

| 2 pollici (51 mm) | 275 µm | 1969 | ||

| 3 pollici (76 mm) | 375 μm | 1972 | ||

| 4-inch (100 mm) | 525 μm | 1976 | 10 grams | 56 |

| 4.9 inch (125 mm) | 625 μm | 1981 | ||

| 150 mm (5.9 inch, usually referred to as “6 inch”) | 675 μm | 1983 | ||

| 200 mm (7.9 inch, usually referred to as “8 inch”) | 725 μm. | 1992 | 53 grams | 269 |

| 300 mm (11.8 pollici, di solito indicato come “12 pollici”) | 775 µm | 2002 | 125 grammi | 640 |

| 450 mm (17.7 inch) (proposta) | 925 µm | – | 342 grammi | 1490 |

| 675 millimetri (26.6 in) (teorica) | Sconosciuto. | – |

I wafer coltivati con materiali diversi dal silicio avranno spessori diversi da quelli di un wafer di silicio dello stesso diametro. Lo spessore del wafer è determinato dalla resistenza meccanica del materiale utilizzato; il wafer deve essere abbastanza spesso da sostenere il proprio peso senza fessurazioni durante la manipolazione. Gli spessori tabulati si riferiscono a quando è stato introdotto quel processo e non sono necessariamente corretti attualmente, ad esempio il processo IBM BiCMOS7WL è su 8 in wafer, ma questi sono spessi solo 200um. Il peso del wafer sale insieme al suo spessore e diametro.

Aumenti storici della dimensione del waferedit

Una fase di fabbricazione di wafer unitari, come una fase di incisione, può produrre più chip proporzionali all’aumento dell’area del wafer, mentre il costo della fase di fabbricazione dell’unità aumenta più lentamente rispetto all’area del wafer. Questa era la base di costo per aumentare le dimensioni del wafer. La conversione in wafer da 300 mm da wafer da 200 mm è iniziata sul serio nel 2000 e ha ridotto il prezzo per die di circa il 30-40%. Wafer di diametro maggiore consentono più die per wafer.

PhotovoltaicEdit

La dimensione del wafer M1 (156,75 mm) è in fase di eliminazione in Cina a partire dal 2020. È sorto un certo numero di dimensioni non standard, quindi gli sforzi per produrre lo standard M10 (182 mm) sono uno sforzo continuo. Come semiconductor cousin, la riduzione dei costi è il principale driver nonostante i requisiti di purezza siano completamente diversi.

Proposta di transizione di 450 mmmodifica

Nonostante il possibile miglioramento della produttività, vi è una notevole resistenza alla transizione di 450 mm, a causa della preoccupazione per l’insufficiente ritorno sull’investimento. Ci sono anche problemi relativi a una maggiore variazione di wafer inter-die / edge-to-edge e ulteriori difetti del bordo. ci si aspetta che i wafer da 450 mm costeranno 4 volte quanto i wafer da 300 mm e che i costi delle attrezzature aumenteranno dal 20 al 50%. Apparecchiature di fabbricazione di semiconduttori a costi più elevati per wafer più grandi aumentano il costo di fab da 450 mm (impianti di fabbricazione di semiconduttori o fabbriche). Il litografo Chris Mack ha affermato nel 2012 che il prezzo complessivo per die per wafer da 450 mm sarebbe stato ridotto solo del 10-20% rispetto ai wafer da 300 mm, poiché oltre il 50% dei costi totali di lavorazione dei wafer sono legati alla litografia. La conversione in wafer più grandi da 450 mm ridurrebbe il prezzo per die solo per operazioni di processo come etch in cui il costo è correlato al numero di wafer, non all’area del wafer. Costo per processi come la litografia è proporzionale alla superficie wafer, e wafer più grandi non ridurrebbe il contributo litografia a morire costo. Nikon ha pianificato di fornire apparecchiature per litografia da 450 mm nel 2015, con produzione in volume nel 2017. Nel novembre 2013 ASML ha messo in pausa lo sviluppo di apparecchiature per litografia da 450 mm, citando tempi incerti della domanda del produttore di chip.

La timeline per 450 mm non è stata corretta. Nel 2012, si prevedeva che la produzione di 450 mm sarebbe iniziata nel 2017, cosa che non è mai stata realizzata. Mark Durcan, allora CEO di Micron Technology, ha dichiarato a febbraio 2014 che si aspetta che l’adozione di 450 mm venga ritardata indefinitamente o interrotta. “Non sono convinto che 450mm accadrà mai, ma, nella misura in cui lo fa, è una lunga via d’uscita in futuro. Non c’è molta necessità per Micron, almeno nei prossimi cinque anni, di spendere un sacco di soldi su 450mm. C’è un sacco di investimenti che devono andare avanti nella comunità delle apparecchiature per farlo accadere. E il valore alla fine della giornata – in modo che i clienti comprassero quell’attrezzatura – penso sia dubbio.”A partire da marzo 2014, Intel Corporation prevede la distribuzione di 450 mm entro il 2020 (entro la fine di questo decennio). Mark LaPedus della semiingegneria.com ha riferito a metà del 2014 che i produttori di chip avevano ritardato l’adozione di 450 mm “per il prossimo futuro.”Secondo questo rapporto alcuni osservatori si aspettavano 2018 a 2020, mentre G. Dan Hutcheson, amministratore delegato di VLSI Research, non ha visto i fab 450mm entrare in produzione fino a 2020 a 2025.

Il passo fino a 300 mm richiedeva grandi cambiamenti, con fabbriche completamente automatizzate che utilizzavano wafer da 300 mm rispetto a fabbriche appena automatizzate per i wafer da 200 mm, in parte perché un FOUP per wafer da 300 mm pesa circa 7,5 chilogrammi quando caricato con 25 wafer da 300 mm dove uno SMIF pesa circa 4.8 chilogrammi quando caricato con 25 200 mm wafer, richiedendo così il doppio della quantità di forza fisica da parte degli operai, e aumentando la fatica. 300mm FOUPs hanno maniglie in modo che possano essere ancora essere spostato a mano. i FOUP da 450 mm pesano 45 chilogrammi se caricati con 25 wafer da 450 mm, pertanto sono necessarie gru per gestire manualmente i FOUP e le maniglie non sono più presenti nel FOUP. FOUPs vengono spostati utilizzando sistemi di movimentazione dei materiali da Muratec o Daifuku. Questi importanti investimenti sono stati intrapresi nella crisi economica dopo la bolla dot-com, con conseguente enorme resistenza all’aggiornamento a 450 mm entro il periodo di tempo originale. Sulla rampa – fino a 450 mm, i lingotti di cristallo saranno 3 volte più pesanti (peso totale di una tonnellata metrica) e impiegheranno 2-4 volte più tempo per raffreddarsi e il tempo di processo sarà doppio. Tutto sommato, lo sviluppo di wafer da 450 mm richiede ingegneria significativa, tempo e costi da superare.

Stima analitica del conteggio degli stampi

Al fine di ridurre al minimo il costo per stampo, i produttori desiderano massimizzare il numero di stampi che possono essere realizzati da un singolo wafer; gli stampi hanno sempre una forma quadrata o rettangolare a causa del vincolo del taglio dei wafer. In generale, questo è un problema computazionalmente complesso senza soluzione analitica, dipendente sia dall’area degli stampi che dal loro rapporto di aspetto (quadrato o rettangolare) e da altre considerazioni come la larghezza della scribeline o della corsia della sega e lo spazio aggiuntivo occupato dall’allineamento e dalle strutture di prova. Si noti che le formule DPW gross rappresentano solo l’area del wafer persa perché non può essere utilizzata per realizzare matrici fisicamente complete; i calcoli DPW gross non tengono conto della perdita di resa dovuta a difetti o problemi parametrici.

Tuttavia, il numero di lordo die per wafer (DPW) può essere stimato a partire con il primo ordine di approssimazione o cialda-per-morire rapporto,

D P W = ⌊ π d 2 4 S ⌋ {\displaystyle DPW=\left\lfloor {\frac {\pi d^{2}}{4S}}\right\rfloor }

d {\displaystyle d}

è il wafer di diametro (in genere in mm) e S {\displaystyle S}

la dimensione di ogni dado (mm2) la larghezza della scribeline (o nel caso di una corsia di sega, il taglio più una tolleranza). Questa formula afferma semplicemente che il numero di matrici che possono stare sul wafer non può superare l’area del wafer diviso per l’area di ogni singolo die. Sopravvaluterà sempre il vero DPW lordo best-case, poiché include l’area delle matrici parzialmente modellate che non si trovano completamente sulla superficie del wafer (vedi figura). Questi stampi parzialmente modellati non rappresentano circuiti integrati completi, quindi non possono essere venduti come parti funzionali.

I perfezionamenti di questa semplice formula in genere aggiungono una correzione del bordo, per tenere conto degli stampi parziali sul bordo, che in generale saranno più significativi quando l’area dello stampo è grande rispetto all’area totale del wafer. Nell’altro caso limite (matrici infinitesimalmente piccole o wafer infinitamente grandi), la correzione del bordo è trascurabile.

Il fattore di correzione o il termine di correzione assume generalmente una delle forme citate da De Vries:

D P W = π d 2 4 S − π d 2 S {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}-{\frac {\displaystyle \pi d}{\sqrt {2}}}}

(rapporto circonferenza/(die lunghezza diagonale)) o D P W = ( π d 2 4 S ) exp ( − 2 S / d ) {\displaystyle DPW=\left({\frac {\displaystyle \pi d^{2}}{4S}}\right)\exp(-2{\sqrt {S}}/d)}

(area di rapporto di scala da un fattore esponenziale) o D P W = π d 2 4 S ( 1 − 2 S d ) 2 {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}\left(1-{\frac {\displaystyle 2{\sqrt {S}}}{d}}\right)^{2}}

(coefficiente ridotto di un fattore polinomiale).

gli Studi che confrontano queste le formule analitiche di tipo brute-force risultati di calcolo mostrano che le formule possono essere più preciso, più pratico intervalli di morire dimensioni e proporzioni, regolando i coefficienti delle correzioni di valori al di sopra o al di sotto dell’unità, e sostituendo la lineare morire dimensione S {\displaystyle {\sqrt {S}}}

con ( H + L ) / 2 {\displaystyle (H+L)/2}

(media lunghezza), nel caso di matrici con grande rapporto di aspetto: D P W = π d 2 4 S − 0.58 ∗ π d S {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}-0.58^{*}{\frac {\displaystyle \pi d}{\sqrt {S}}}}

o D P W = ( π d 2 4 S ) exp ( − 2.32 ∗ S / d ) {\displaystyle DPW=\left({\frac {\displaystyle \pi d^{2}}{4S}}\right)\exp(-2.32^{*}{\sqrt {S}}/d)}

o D P W = π d 2 4 S ( 1 − 1.16 ∗ S d ) 2 {\displaystyle DPW={\frac {\displaystyle \pi d^{2}}{4S}}\left(1-{\frac {\displaystyle 1.16^{*}{\sqrt {S}}}{d}}\right)^{2}}

.

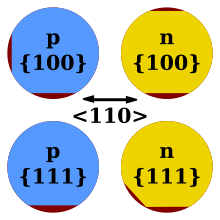

Cristallina orientationEdit

I wafer sono ottenuti da cristalli aventi una struttura cristallina regolare, con silicio avente una struttura cubica diamantata con una spaziatura reticolare di 5,430710 Å (0,5430710 nm). Quando tagliato in wafer, la superficie è allineata in una delle diverse direzioni relative note come orientamenti di cristallo. L’orientamento è definito dall’indice Miller con facce (100) o (111) che sono le più comuni per il silicio.L’orientamento è importante poiché molte delle proprietà strutturali ed elettroniche di un singolo cristallo sono altamente anisotropiche. Le profondità di impianto ionico dipendono dall’orientamento del cristallo del wafer, poiché ogni direzione offre percorsi distinti per il trasporto.

La scissione del wafer si verifica in genere solo in alcune direzioni ben definite. Segnare il wafer lungo i piani di scissione permette che sia tagliato facilmente nei singoli chip (“muore”) in moda da potere separare i miliardi degli elementi del singolo circuito su un wafer medio in molti circuiti individuali.

Tacche di orientamento cristallograficomodifica

I wafer di diametro inferiore a 200 mm hanno piani tagliati in uno o più lati che indicano i piani cristallografici del wafer (di solito una faccia {110}). Nei wafer di prima generazione una coppia di piatti ad angoli diversi ha inoltre trasmesso il tipo di doping (vedi illustrazione per le convenzioni). I wafer di diametro pari o superiore a 200 mm utilizzano un’unica piccola tacca per trasmettere l’orientamento del wafer, senza alcuna indicazione visiva di tipo drogante.

Impurità dopingEdit

I wafer di silicio non sono generalmente silicio puro al 100%, ma sono invece formati con una concentrazione iniziale di drogaggio di impurità tra 1013 e 1016 atomi per cm3 di boro, fosforo, arsenico o antimonio che viene aggiunto al fuso e definisce il wafer come massa di tipo n o di tipo P. Tuttavia, rispetto alla densità atomica del silicio monocristallino di 5 × 1022 atomi per cm3, questo dà ancora una purezza superiore al 99,9999%. I wafer possono anche essere inizialmente forniti con una certa concentrazione di ossigeno interstiziale. Carbonio e contaminazione metallica sono ridotti al minimo. I metalli di transizione, in particolare, devono essere mantenuti al di sotto delle parti per miliardo di concentrazioni per applicazioni elettroniche.